与分立器件相比,现代集成运算放大器(op amp)和仪表放大器(in-amp)为设计工程师带来了许多好处。虽然提供了许多巧妙、有用并且吸引人的电路。往往都是这样,由于仓促地组装电路而会忽视了一些非常基本的问题,从而导致电路不能实现预期功能 – 或者可能根本不工作。本文将讨论一些最常见的应用问题,并给出实用的解决方案。

AC耦合时缺少DC偏置电流回路

最常遇到的一个应用问题是在交流(AC)耦合运算放大器或仪表放大器电路中没有提供偏置电流的直流(DC)回路。在图1中,一只电容器与运算放大器的同相输入端串联以实现AC耦合,这是一种隔离输入电压(VIN)的DC分量的简单方法。这在高增益应用中尤其有用,在那些应用中哪怕运算放大器输入端很小的直流电压都会限制动态范围,甚至导致输出饱和。然而,在高阻抗输入端加电容耦合,而不为同相输入端的电流提供DC通路,会出现问题。

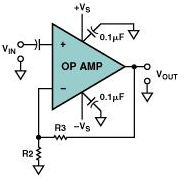

图1.错误的运算放大器AC耦合输入

实际上,输入偏置电流会流入耦合的电容器,并为它充电,直到超过放大器输入电路的共模电压的额定值或使输出达到极限。根据输入偏置电流的极性,电容器会充电到电源的正电压或负电压。放大器的闭环DC增益放大偏置电压。

这个过程可能会需要很长时间。例如,一只场效应管(FET)输入放大器,当1 pA的偏置电流与一个0.1μF电容器耦合时,其充电速率I/C为10–12/10–7=10 μV/s,或每分钟600μV。如果增益为100,那么输出漂移为每分钟0.06 V。因此,一般实验室测试(使用AC耦合示波器)无法检测到这个问题,而电路在数小时之后才会出现问题。显然,完全避免这个问题非常重要。

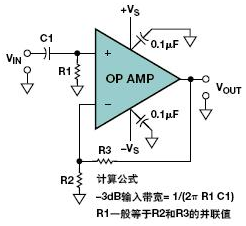

图2.正确的双电源供电运算放大器AC耦合输入方法

图2示出了对这常见问题的一种简单的解决方案。这里,在运算放大器输入端和地之间接一只电阻器,为输入偏置电流提供一个对地回路。为了使输入偏置电流造成的失调电压最小,当使用双极性运算放大器时,应该使其两个输入端的偏置电流相等,所以通常应将R1的电阻值设置成等于R2和R3的并联阻值。

然而,应该注意的是,该电阻器R1总会在电路中引入一些噪声,因此要在电路输入阻抗、输入耦合电容器的尺寸和电阻器引起的Johnson噪声之间进行折衷。典型的电阻器阻值一般在100,000Ω ~1 MΩ之间。

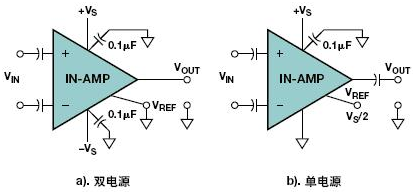

类似的问题也会出现在仪表放大器电路中。图3示出了使用两只电容器进行AC耦合的仪表放大器电路,没有提供输入偏置电流的返回路径。这个问题在使用双电源(图3a)和单电源(图3b)供电的仪表放大器电路中很常见。

图3.不工作的AC耦合仪表放大器实例

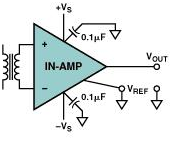

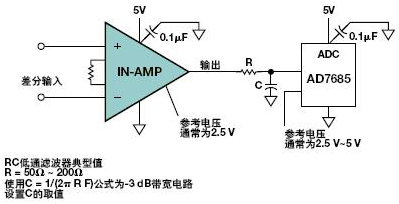

这类问题也会出现在变压器耦合放大器电路中,如图4所示,如果变压器次级电路中没有提供DC对地回路,该问题就会出现。

图4.不工作的变压器耦合仪表放大器电路

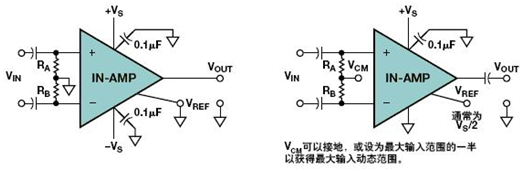

图5和图6示出了这些电路的简单解决方案。这里,在每一个输入端和地之间都接一个高阻值的电阻器(RA,BR)。这是一种适合双电源仪表放大器电路的简单而实用的解决方案。

图5.每个输入端与地之间都接一个高阻值的电阻器以提供必需的偏置电流回路。

a.双电源. b.单电源.

这两只电阻器为输入偏置电流提供了一个放电回路。在图5所示的双电源例子中,两个输入端的参考端都接地。在图5b所示的单电源例子中,两个输入端的参考端或者接地(VCM接地)或者接一个偏置电压,通常为最大输入电压的一半。

同样的原则也可以应用到变压器耦合输入电路(见图6),除非变压器的次级有中间抽头,它可以接地或接VCM。

在该电路中,由于两只输入电阻器之间的失配和(或)两端输入偏置电流的失配会产生一个小的失调电压误差。为了使失调误差最小,在仪表放大器的两个输入端之间可以再接一只电阻器(即桥接在两只电阻器之间),其阻值大约为前两只电阻器的1/10(但与差分源阻抗相比仍然很大)

图6.正确的仪表放大器变压器输入耦合方法

为仪表放大器、运算放大器和ADC提供参考电压

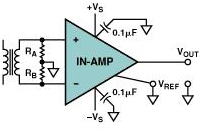

图7示出一个仪表放大器驱动一个单端输入的模数转换器(ADC)的单电源电路。该放大器的参考电压提供一个对应零差分输入时的偏置电压,而ADC的参考电压则提供比例因子。在仪表放大器的输出端和ADC的输入端之间通常接一个简单的RC低通抗混叠滤波器以减少带外噪声。设计工程师通常总想采用简单的方法,例如电阻分压器,为仪表放大器和ADC提供参考电压。因此在使用某些仪表放大器时,会产生误差。

图7.仪表放大器驱动ADC的典型单电源电路

正确地提供仪表放大器的参考电压

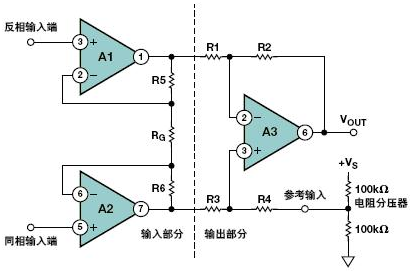

一般假设仪表放大器的参考输入端为高阻抗,因为它是一个输入端。所以使设计工程师一般总想在仪表放大器的参考端引脚接入一个高阻抗源,例如一只电阻分压器。这在某些类型仪表放大器的使用中会产生严重误差(见图8)。

图8.错误地使用一个简单的电阻分压器直接驱动3运放仪表放大器的参考电压引脚

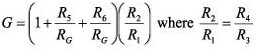

例如,流行的仪表放大器

设计配置使用上图所示的三运放结构。其信号总增益为

参考电压输入端的增益为1(如果从低阻抗电压源输入)。但是,在上图所示的电路中,仪表放大器的参考输入端引脚直接与一个简单的分压器相连。这会改变减法器电路的对称性和分压器的分压比。这还会降低仪表放大器的共模抑制比及其增益精度。然而,如果接入R4,那么该电阻的等效电阻会变小,减小的电阻值等于从分压器的两个并联支路看过去的阻值(50 kΩ),该电路表现为一个大小为电源电压一半的低阻抗电压源被加在原值R4上,减法器电路的精度保持不变。

如果仪表放大器采用封闭的单封装形式(一个IC),则不能使用这种方法。此外,还要考虑分压电阻器的温度系数应该与R4和减法器中的电阻器保持一致。最终,参考电压将不可调。另一方面,如果尝试减小分压电阻器的阻值使增加的电阻大小可忽略,这样会增大电源电流的消耗和电路的功耗。在任何情况下,这种笨拙的方法都不是好的设计方案。

图9示出了一个更好的解决方案,在分压器和仪表放大器参考电压输入端之间加一个低功耗运算放大器缓冲器。这会消除阻抗匹配和温度系数匹配的问题,而且很容易对参考电压进行调节。

图9.利用低输出阻抗运算放大器驱动仪表放大器的参考电压输入端

当从电源电压利用分压器为放大器提供参考电压时应保证PSR性能

一个经常忽视的问题是电源电压VS的任何噪声、瞬变或漂移都会通过参考输入按照分压比经过衰减后直接加在输出端。实际的解决方案包括旁路滤波以及甚至使用精密参考电压IC产生的参考电压,例如ADR121,代替VS分压。

当设计带有仪表放大器和运算放大器的电路时,这方面的考虑很重要。电源电压抑制技术用来隔离放大器免受其电源电压中的交流声、噪声和任何瞬态电压变化的影响。这是非常重要的,因为许多实际电路都包含、连接着或存在于只能提供非理想的电源电压的环境之中。另外电力线中的交流信号会反馈到电路中被放大,而且在适当的条件下会引起寄生振荡。

现代的运算放大器和仪表放大器都提供频率相当低的电源电压抑制(PSR)能力作为其设计的一部分。这在大多数工程师看来是理所当然的。许多现代的运算放大器和仪表放大器的PSR指标在80~100dB以上,可以将电源电压的变化影响衰减到1/10,000~1/100,000。甚至最适度的40 dB PSR的放大器隔离对电源也可以起到1/100的抑制作用。不过,总是需要高频旁路电容(正如图1~7所示)并且经常起到重要作用。

此外,当设计工程师采用简单的电源电压电阻分压器并且用一只运算放大器缓冲器为仪表放大器提供参考电压时,电源电压中的任何变化都会通过该电路不经衰减直接进入仪表放大器的输出级。因此,除非提供低通滤波器,否则IC通常优良的PSR性能会丢失。

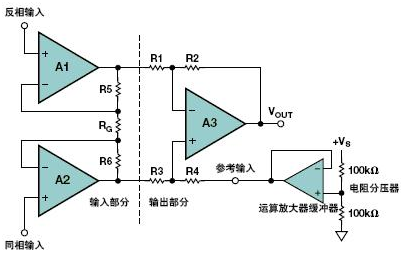

在图10中,在分压器的输出端增加一个大电容器以滤除电源电压的变化并且保证PSR性能。滤波器的-3 dB极点由电阻器R1/R2并联和电容器C1决定。-3 dB极点应当设置在最低有用频率的1/10处。

图10.保证PSR性能的参考端退耦电路

上面示出的CF试用值能够提供大约0.03 Hz的–3 dB极点频率。接在R3两端的小电容器(0.01 μF)可使电阻器噪声最小。

该滤波器充电需要时间。按照试用值,参考输入的上升时间应是时间常数的几倍(这里T=R3Cf= 5 s),或10~15s。

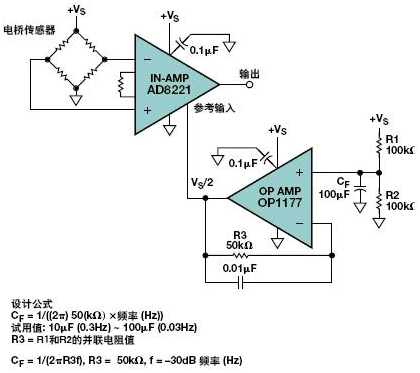

图11中的电路做了进一步改进。这里,运算放大器缓冲器起到一个有源滤波器的作用,它允许使用电容值小很多的电容器对同样大的电源退耦。此外,有源滤波器可以用来提高Q值从而加快导通时间。

图11.将运算放大器缓冲器接成有源滤波器驱动仪表放大器的参考输入引脚

测试结果:利用上图所示的元件值,施加12 V电源电压,对仪表放大器的6 V参考电压提供滤波。将仪表放大器的增益设置为1,采用频率变化的1 VP-P正弦信号调制12 V电源。在这样的条件下,随着频率的减小,一直减到大约8 Hz时,我们在示波器上看不到AC信号。当对仪表放大器施加低幅度输入信号时,该电路的测试电源电压范围是4 V到25 V以上。电路的导通时间大约为2 s。

单电源运算放大器电路的退耦

最后,单电源运算放大器电路需要偏置共模输入电压幅度以控制AC信号的正向摆幅和负向摆幅。当从电源电压利用分压器提供偏置电压时,为了保证PSR的性能就需要合适的退耦。

一种常用但不正确的方法是利用100 kΩ/100 kΩ电阻分压器(加0.1μF旁路电容)提供VS/2给运算放大器的同相输入端。使用这样小的电容值对电源退耦通常是不够的,因为极点仅为32 Hz。电路出现不稳定(“低频振荡”),特别是在驱动感性负载时。

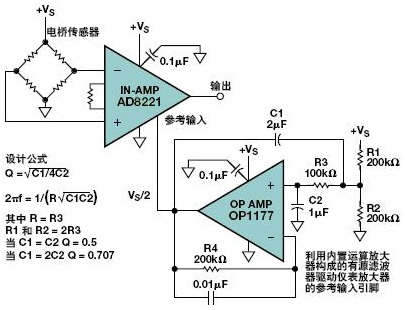

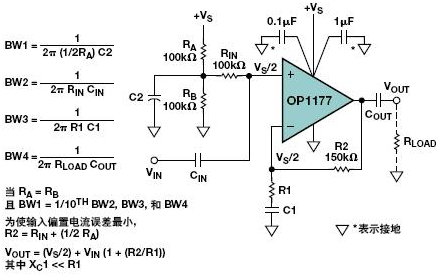

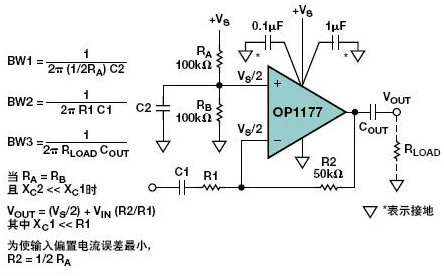

图12(反相输入)和图13(同相输入)示出了达到最佳退耦结果的VS/2偏置电路。在两种情况中,偏置电压加在同相输入端,反馈到反向输入端以保证相同的偏置电压,并且单位DC增益也要偏置相同的输出电压。耦合电容器C1使低频增益从BW3降到单位增益。

图12.单电源同相输入放大器电路正确的电源退耦方案。中频增益=1+R2/R1

如上图所示,当采用100 kΩ/100 kΩ电阻分压器时一个好的经验是,为获得0.3 Hz的–3 dB截止频率,应当选用的C2最小为10 ΩF,。而100 μF(0.03 Hz)实际上对所有电路都足够了。

图13.单电源反相输入放大器正确的退耦电路,中频增益= – R2/R1