1、ARM汇编:汇编中IA、IB、DA、DB和FD、ED、FA、EA

2、ARM处理器的9种模式详解

3、MRS,MSR指令详解

4、嵌入式DDR布线分析 DDR信号布线介绍

5、嵌入式学习之IRQ和FIQ之间的区别

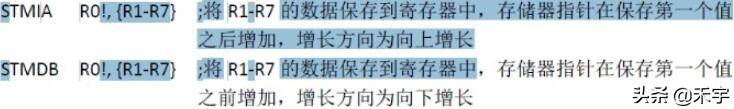

ARM指令的多数据传输(STM、LDM)中,提到:多寄存器的Load和Store指令分为2组:一组用于数据的存储与读取,对应于IA、IB、DA、DB,一组用于堆栈操作,对应于FD、ED、FA、EA,

两组中对应的指令含义相同。

IA:increase after ;表示数据传输后地址增加IB:increase beforeDA: decrease afterDB: decrease before

即:

上述各组2个指令含义相同只是适用场合不同,同理有:

1、LDMIB、LDMED;

2、LDMIA、LDMFD;

3、LDMDB、LDMEA

4、LDMDA、LDMFA。

IA模式表示:每次传送后地址 4;(After Increase)

DB模式表示:每次传送前地址-4;(Before Decrease)

多寄存器加载/存储指令共有8种模式(4个用与数据块的传输,4个用于栈操作)

STMDB和LDMIA指令一般配对使用,STMDB用于将寄存器压栈,LDMIA用于将寄存器弹出栈,作用是保存使用到的寄存器。

例、

指令:stmdb sp!,{r0-r12,lr}含义:sp = sp - 4,先压lr,sp = lr(即将lr中的内容放入sp所指的内存地址)。sp = sp - 4,再压r12,sp = r12。sp = sp - 4,再压r11,sp = r11......sp = sp - 4,最后压r0,sp = r0。

如果想要将r0-r12和lr弹出,可以用ldmia指令:ldmia sp!,{r0-r12,lr}例

STMIA, 比如当前r0指向的内存地址是 0x1000,STMIA R0!,{R1-R7} 就是 首先把r1存入 0x1000,然后r2存入0x1004,然后r3存入0x1008,如果是32位的处理器就是每次加4个字节,以此类推把 r1-r7按照递增的地址存入,这个r0!就是从r0的地址开始存的意思。STMDB则是地址从r0开始减少,依次存储。

例

LDMIA:LDM是多寄存器存取的意思,后面参数以“,”分隔,第一个参数是首地址;第二个参数是寄存器列表,并以“{}”括起来。LDMIA R0!, {R1-R4};R0表示要操作的存储空间首地址,要操作的数据个数由寄存器列表决定,现在是R1到R4,共4个数据(每个数据是32bits的)

具体:地址为R0的存储空间中的数据赋值给R1地址为R0 4的存储空间中的数据赋值给R2地址为R0 8的存储空间中的数据赋值给R3地址为R0 12的存储空间中的数据赋值给R4

所有的示例指令执行前的存储空间和寄存器情况:mem32[0x1000C] = 0x04mem32[0x10008] = 0x03mem32[0x10004] = 0x02mem32[0x10000] = 0x01r0 = 0x00010000r1 = 0x00000000r3 = 0x00000000r4 = 0x00000000执行后存储空间不变,寄存器变化:r0 = 0x00010010r1 = 0x01r2 = 0x02r3 = 0x03r4 = 0x04

2、ARM处理器的9种模式详解

ARM的处理器模式分几种要看是ARM的哪个系列,但是以现在的系列来说,有九种模式,这九种模式就是CPU在运算的时候,本来在读程序,突然系统发生异常,比如说蓝屏,这个时候操作系统肯定有相关的处理,同时我们也需要CPU一些信号,那么我们就可以通话CPU的切换来进行处理,这样实际上是在最低级别上考虑到的方式来完成了安全控制和效率控制,还有节能控制,所以这就是我们为什么要模式切换的原因,它模式与模式之间相对而言是比较独立的。

Cortex-A九种处理器模式

1,user模式:用户模式,大部分程序运行时候的非特权模式。

2,FIQ模式:快速中断模式,进入FIQ中断异常,中断也会分类,除了硬件中断还有软件中断,中断的时候也会有消息传过来,这个消息可能数据量比较大,而且要求还很大,还有的消息数据量比较小,它要求就会很小,这种要求大的中断我们就称为快速中断,比较小的我们就称为一般中断。

3,IRQ模式:一般中断模式。

4,Supervisor(SVC)模式:超级管理员,它主要是用来管理调用指令被执行或者reset的时候,这个模式的权限级别非常大,所以一般情况下是不能随便用的。

5,Monitor(MON)模式:监视模式,就像后台服务,就像监测网络信号,其实CPU不需要去处理一些用户中断,这个模式主要用来安全扩展模式,只用于安全。

6,Abort(ABY)模式:退出模式,通常开始发生了用户级别的开始,就会出现这样的退出,这个时候CPU就会说暂停下面的代码运行,就直接退出。

7,Hyp(HYP)模式:是一个超级的监视者,它比超级管理员要稍微低一点,它主要是用来做一些虚拟化的扩展。

8,Undef(UND)模式:它就是未定义的指令执行的时候,比如说一条指令是CPU不识别的,就叫做未定义。

9,System(SYS)模式:系统模式,当系统自己异常的时候,就会发生这样的模式,它有一个特点就是可以进行各个模式的切换,在不同的状态的时候,访问的寄存器就有可能不一样,这个模式用到的寄存器与用户模式是共享的,只是访问级别不一样。这九种模式里面User模式称为非特权模式,其他的全部称为特权模式。

3、MRS,MSR指令详解

在ARM处理器中,只有MRS(Move to Register from State register)指令可以对状态寄存器CPSR和SPSR进行读操作。通过读CPSR可以获得当前处理器的工作状态。读SPSR寄存器可以获得进入异常前的处理器状态(因为只有异常模式下有SPSR寄存器)。

例如:

MRS R1,CPSR ; 将CPSR状态寄存器读取,保存到R1中

MRS R2,SPSR ; 将SPSR状态寄存器读取,保存到R2中

通过MRS指令可以取得状态寄存器里的值,然后比较其模式位M[4:0]的值判断当前所处模式,当然也可以比较其它相应位了解当前CPU的状态。

同样,在ARM处理器中,只有MSR指令可以对状态寄存器CPSR和SPSR进行写操作。与MRS配合使用,可以实现对CPSR或SPSR寄存器的读-修改-写操作,可以切换处理器模式、或者允许/禁止IRQ/FIQ中断等。

由于xPSR寄存器代表了CPU的状态,其每个位有特殊意义,在执行对xPSR状态寄存器写入时(读取时不存在该用法),为了防止误操作和方便记忆,将xPSR里32位分成四个区域,每个区域用小写字母表示:

c 控制域屏蔽 psr[7..0]

x 扩展域屏蔽 psr[15..8]

s 状态域屏蔽 psr[23..16]

f 标志域屏蔽 psr[31..24]

注意:区域名必须为小写字母

向对应区域进行执行写入时,使用xPSR_x可以指定写入区域,而不影响状态寄存器其它位,如:

使能IRQ中断:

ENABLE_IRQ

MRS R0, CPSR ; 将CPSR寄存器内容读出到R0

BIC R0, R0,#0x80 ; 清掉CPSR中的I控制位

MSR CPSR_c,R0 ; 将修改后的值写回 CPSR寄存器的对应控制域

MOV PC,LR ; 返回上一层函数

禁用IRQ中断:

DISABLE_IRQ

MRS R0 CPSR ; 将CPSR寄存器内容读出到R0

ORR R0, R0,#0x80 ; 设置CPSR中的I控制位

MSR CPSR_c,R0 ; 将修改后的值写回 CPSR寄存器的对应控制域

MOV PC,LR ; 返回上一层函数

下表列出了不同模式的二进制数表示:

表3-3 不同工作模式对应二进制

在对开发板进行初始化时,用对不同模式指定其栈空间,下面例子对各模式的栈指针sp进行初始化:

stack_init ; 栈指针初始化函数

@ undefine_stack

msr cpsr_c, #0xdb ; 切换到未定义异常

ldr sp, =0x34000000 ; 栈指针为内存最高地址,栈为倒生的栈

; 栈空间的最后1M 0x34000000~0x33f00000

@ abort_stack

msr cpsr_c, #0xd7 ; 切换到终止异常模式

ldr sp, =0x33f00000 ; 栈空间为1M,0x33f00000~0x33e00000

@ irq_stack

msr cpsr_c, #0xd2 ; 切换到中断模式

ldr sp, =0x33e00000 ; 栈空间为1M,0x33e00000~0x33d00000

@ sys_stack

msr cpsr_c, #0xdf ; 切换到系统模式

ldr sp, =0x33d00000 ; 栈空间为1M,0x33d00000~0x33c00000

msr cpsr_c, #0xd3 ; 切换回管理模式

mov pc, lr

4、嵌入式DDR布线分析 DDR信号布线介绍

嵌入式DDR(Double Data Rate,双数据速率)设计是含DDR的嵌入式硬件设计中最重要和最核心的部分。随着嵌入式系统的处理能力越来越强大,实现的功能越来越多,系统的工作频率越来越高,DDR的工作频率也逐渐从最低的133 MHz提高到200 MHz,从而实现了更大的系统带宽和更好的性能。然而,更高的工作频率同时也对系统的稳定性提出了更高的要求,这需要硬件设计者对电路的布局走线有更多的约束和考虑。而影响整个系统能否工作正常且稳定的最重要的部分就是DDR部分的电路设计。

嵌入式系统使用DDR内存,可以在传统的单数据数率内存芯片上实现更好的性能。DDR允许在不增加时钟频率和数据位宽的条件下,一个时钟周期内能够处理两个操作。增加的数据总线性能是由于源同步数据选通允许数据同时在选通脉冲的上升沿和下降沿被获取

DDR虽然能够给嵌入式设计带来更好的性能,但是设计者必须比以往的SDR设计更小心地处理DDR部分的PCB布线部分,否则不仅不能实现好的性能,整个嵌人式系统的稳定性也会受到影响。DDR比传统的SDR有更短的信号建立保持时间、更干净的参考电压、更紧密的走线匹配和新的I/O口信号,并且需要合适的终端电阻匹配。这些都是要面对的新的挑战。

对于DDR内存,JEDEC建立和采用了一个低压高速信号标准。这个标准称为“短截线串联终结逻辑(StubSeries Terminated Logic,SSTL)”。SSTL能够改进数据通过总线传输的信号完整性,这种终端设计的目的是防止在高速传输下由于信号反射导致的数据错误。

在一个典型的内存拓扑结构中,如果使用了串联匹配电阻(RS),那么它应该放在远离DDR控制器的位置。这种方法能够节约控制器附近宝贵的电路板空间,避免布线拥塞和繁琐的引脚扇出;而且也优化了从控制器到内存芯片的信号完整性,在这些位置往往有很多地址和命令信号需要可靠地被多个内存接收。

最普通的SSTL终端模型是一种较好的单终端和并联终端方案,如图1所示。这种方案包含使用一个串联终端电阻(Rs)从控制器到内存,以及一个并联终端电阻(RT)上拉到终端电压(VTT)。这种方法常见于商用电脑的主板上,但目前的嵌入式主板上为了获得更好的信号完整性和系统稳定性,也常常使用。RS和RT的值是信赖于具体的系统的,应该由板级仿真确定具体的值。

5、嵌入式学习之IRQ和FIQ之间的区别

IRQ和FIQ是ARM处理器的两种编程模式。IRQ是指中断模式,FIR是指快速中断模式。对于 FIQ 你必须尽快处理你的事情并离开这个模式。IRQ 可以被 FIQ 所中断,但 IRQ 不能中断 FIQ。为了使 FIQ 更快,所以这种模式有更多的影子寄存器。FIQ 不能调用 SWI(软件中断)。FIQ 还必须禁用中断。如果一个 FIQ 例程必须重新启用中断,则它太慢了,并应该是 IRQ 而不是 FIQ。

对FIQ你必须进快处理中断请求,并离开这个模式。

IRQ可以被FIQ所中断,但FIQ不能被IRQ所中断。在处理FIQ时必须要关闭中断。

FIQ和IRQ是两种不同类型的中断,ARM为了支持这两种不同的中断,提供了对应的叫做FIQ和IRQ处理器模式(ARM有7种处理模式)。

一般的中断控制器里我们可以配置与控制器相连的某个中断输入是FIQ还是IRQ,所以一个中断是可以指定为FIQ或者IRQ的,为了合理,要求系统更快响应,自身处理所耗时间也很短的中断设置为FIQ,否则就设置了IRQ。

如果该中断设置为了IRQ,那么当该中断产生的时候,中断处理器通过IRQ请求线告诉ARM,ARM就知道有个IRQ中断来了,然后ARM切换到IRQ模式运行。类似的如果该中断设置为FIQ,那么当该中断产生的时候,中断处理器通过FIQ请求线告诉ARM,ARM就知道有个FIQ中断来了,然后切换到FIQ模式运行。

简单的对比的话就是FIQ比IRQ快,为什么快呢?

ARM的FIQ模式提供了更多的banked寄存器,r8到r14还有SPSR,而IRQ模式就没有那么多,R8,R9,R10,R11,R12对应的banked的寄存器就没有,这就意味着在ARM的IRQ模式下,中断处理程序自己要保存R8到R12这几个寄存器,然后退出中断处理时程序要恢复这几个寄存器,而FIQ模式由于这几个寄存器都有banked寄存器,模式切换时CPU自动保存这些值到banked寄存器,退出FIQ模式时自动恢复,所以这个过程FIQ比IRQ快.

FIQ比IRQ有更高优先级,如果FIQ和IRQ同时产生,那么FIQ先处理。

在symbian系统里,当CPU处于FIQ模式处理FIQ中断的过程中,预取指令异常,未定义指令异常,软件中断全被禁止,所有的中断被屏蔽。所以FIQ就会很快执行,不会被其他异常或者中断打断,所以它又比IRQ快了。而IRQ不一样,当ARM处理IRQ模式处理IRQ中断时,如果来了一个FIQ中断请求,那正在执行的IRQ中断处理程序会被抢断,ARM切换到FIQ模式去执行这个FIQ,所以FIQ比IRQ快多了。

另外FIQ的入口地址是0x1c,IRQ的入口地址是0x18。